Viện Kỹ sư Bán dẫn Hàn Quốc vừa chính thức công bố một lộ trình đầy tham vọng mang tên “Lộ trình Công nghệ Bán dẫn 2026”, trong đó đưa ra những dự báo quan trọng về sự phát triển của vật liệu silicon trong 15 năm tiếp theo. Trong bối cảnh Samsung chỉ mới vừa công bố dòng chipset 2nm sử dụng công nghệ GAA đầu tiên trên thế giới là Exynos 2600, các chuyên gia đã mạnh dạn dự đoán rằng đến năm 2040, các mạch bán dẫn sẽ thu nhỏ xuống mức không tưởng là 0.2nm, chính thức đưa nhân loại bước vào kỷ nguyên Angstrom (A). Tuy nhiên, để hiện thực hóa giấc mơ này, ngành công nghiệp sẽ phải trải qua một chặng đường dài đầy chông gai với vô số rào cản kỹ thuật cần vượt qua.

Lộ trình phát triển công nghệ bán dẫn (chip 2nm) và kỷ nguyên Angstrom

Báo cáo từ trang tin ETNews cho biết mục đích cốt lõi của lộ trình này là nhằm góp phần củng cố công nghệ bán dẫn dài hạn và năng lực cạnh tranh của ngành công nghiệp, đồng thời kích hoạt các nghiên cứu học thuật và thiết lập các chiến lược phát triển nguồn nhân lực chất lượng cao. Lộ trình do Viện Kỹ sư Bán dẫn trình bày bao gồm chín công nghệ cốt lõi, trải dài từ thiết bị và quy trình bán dẫn, chất bán dẫn trí tuệ nhân tạo (AI), kết nối quang học, cảm biến kết nối không dây, cho đến kết nối có dây, công nghệ PI M, quy trình đóng gói và cả điện toán lượng tử.

Hiện tại, công nghệ quang khắc tiên tiến nhất thuộc về quy trình 2nm Gate-All-Around (GAA) của Samsung. Tuy nhiên, gã khổng lồ công nghệ Hàn Quốc được cho là đã lên kế hoạch cho các biến thể tốt hơn của quy trình sản xuất này. Cụ thể, Samsung đã hoàn thành thiết kế cơ bản cho nút 2nm GAA thế hệ thứ hai và đang có kế hoạch triển khai SF2P+, tức công nghệ 2nm GAA thế hệ thứ ba, trong vòng hai năm tới. Samsung, đơn vị hiện đang dẫn đầu tại Hàn Quốc về sản xuất chất bán dẫn thế hệ tiếp theo, cũng được cho là đã thành lập một đội ngũ chuyên biệt để bắt đầu nghiên cứu phát triển chip 1nm, với mục tiêu sản xuất hàng loạt được đặt ra vào năm 2029.

Nhìn xa hơn về tương lai vào năm 2040, các chuyên gia ước tính rằng quy trình 0.2nm sẽ sử dụng một cấu trúc bóng bán dẫn thế hệ mới gọi là CFET (Complementary Field Effect Transistor – Bóng bán dẫn hiệu ứng trường bổ sung) kết hợp với thiết kế 3D nguyên khối (monolithic 3D). Đây là những công nghệ cực kỳ phức tạp, cho phép xếp chồng các thành phần lên nhau để tiết kiệm diện tích và tăng hiệu suất, thay vì chỉ thu nhỏ kích thước theo chiều ngang như truyền thống.

Tương lai của bộ nhớ lưu trữ và sức mạnh trí tuệ nhân tạo

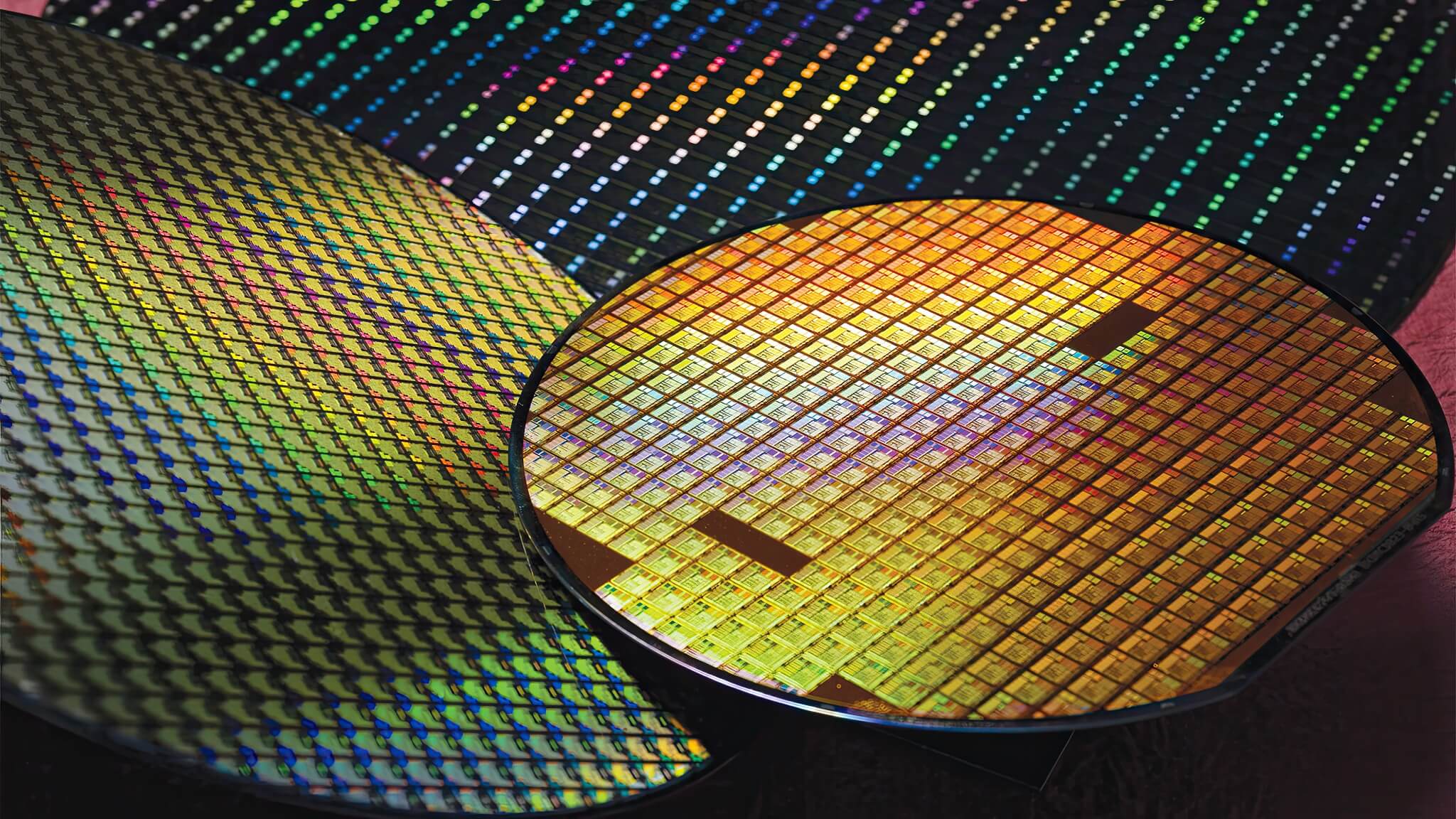

Không chỉ dừng lại ở các bộ vi xử lý trung tâm, lộ trình này còn đưa ra những dự đoán đột phá cho ngành công nghiệp bộ nhớ và chip AI. Những cải tiến này không chỉ được áp dụng cho các vi xử lý di động (SoC) mà còn cho cả bộ nhớ DRAM. Theo đó, mạch bộ nhớ của DRAM dự kiến sẽ được thu nhỏ từ kích thước 11nm hiện nay xuống còn 6nm, giúp tăng mật độ lưu trữ và tốc độ truy xuất dữ liệu.

Đối với bộ nhớ băng thông cao (HBM), vốn đang là thành phần quan trọng trong các hệ thống AI, công nghệ này được báo cáo sẽ có bước tiến vượt bậc. Từ mức 12 lớp xếp chồng với băng thông 2TB/s hiện tại, HBM sẽ phát triển lên tới 30 lớp và đạt băng thông kinh hoàng 128TB/s. Về phần bộ nhớ flash NAND, nơi SK Hynix đã phát triển thành công công nghệ QLC 321 lớp, những tiến bộ trong tương lai sẽ cho phép tạo ra các chip nhớ NAND QLC lên tới 2.000 lớp, mở ra khả năng lưu trữ khổng lồ trong những thiết bị nhỏ gọn.

Cuối cùng là về sức mạnh của các bộ xử lý trí tuệ nhân tạo. Hiện tại, chúng ta đã có các chip AI đạt hiệu suất khoảng 10 TOPS (nghìn tỷ phép tính mỗi giây). Tuy nhiên, báo cáo khẳng định rằng trong một thập kỷ rưỡi nữa, chúng ta có thể sở hữu những con chip có khả năng tạo ra 1.000 TOPS cho các tác vụ học máy (learning) và 100 TOPS cho các tác vụ suy luận (inference). Những con số này vẽ nên một tương lai nơi khả năng tính toán của máy móc sẽ vượt xa trí tưởng tượng của chúng ta ngày nay, nhưng nó cũng đòi hỏi những nỗ lực nghiên cứu không ngừng nghỉ để biến lý thuyết thành hiện thực.