AMD Zen 6 sẽ mang đến bước tiến lớn trong công nghệ kết nối die-to-die (D2D), thay thế phương pháp SERDES truyền thống bằng giải pháp mới mang tên “Sea-of-Wires”, hứa hẹn cải thiện cả hiệu suất năng lượng lẫn độ trễ. Những dấu hiệu đầu tiên của công nghệ này đã được nhìn thấy trong dòng APU Strix Halo.

SERDES: Giới hạn của công nghệ cũ

Trong nhiều thế hệ CPU, AMD đã sử dụng SERDES (serializer/deserializer) để xử lý giao tiếp giữa các chiplet. Cơ chế này cho phép dữ liệu song song từ CCD (Core Complex Dies) được chuyển đổi thành luồng bit tuần tự, rồi truyền qua lớp nền (substrate) đến SoC die. Ở phía nhận, dữ liệu sẽ được giải mã trở lại thành tín hiệu song song.

Tuy nhiên, quá trình này có hai nhược điểm chính. Thứ nhất, việc mã hóa và giải mã đòi hỏi thêm năng lượng cho các tác vụ như phục hồi xung nhịp, cân bằng tín hiệu, và xử lý mã hóa/giải mã. Thứ hai, quá trình chuyển đổi này tạo ra độ trễ đáng kể trong việc truyền dữ liệu giữa các die. Khi nhu cầu kết nối tăng lên cùng với sự xuất hiện của các NPU (Neural Processing Unit), SERDES không còn là giải pháp tối ưu.

Sea-of-Wires: Giải pháp mới trên Strix Halo và Zen 6

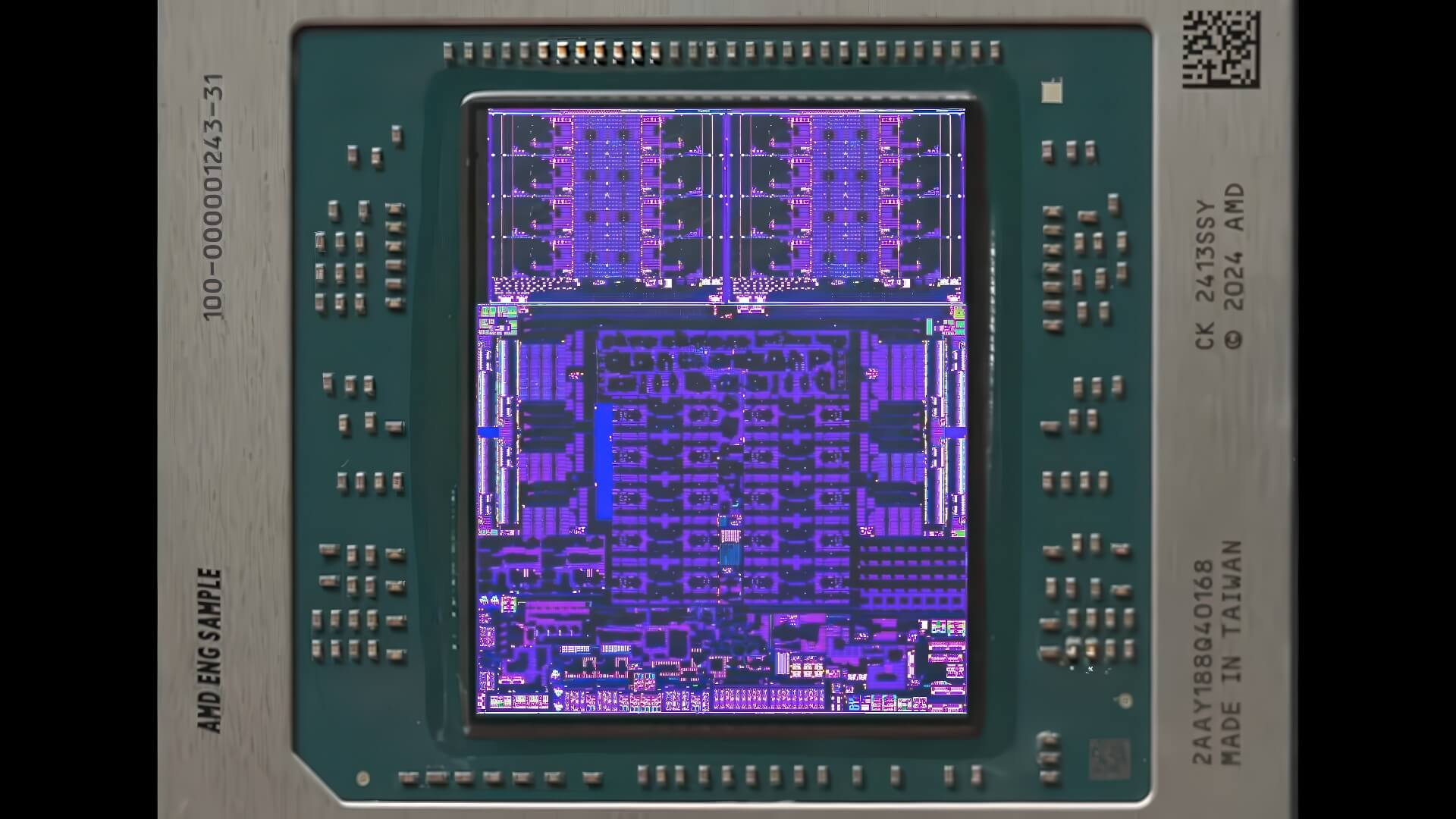

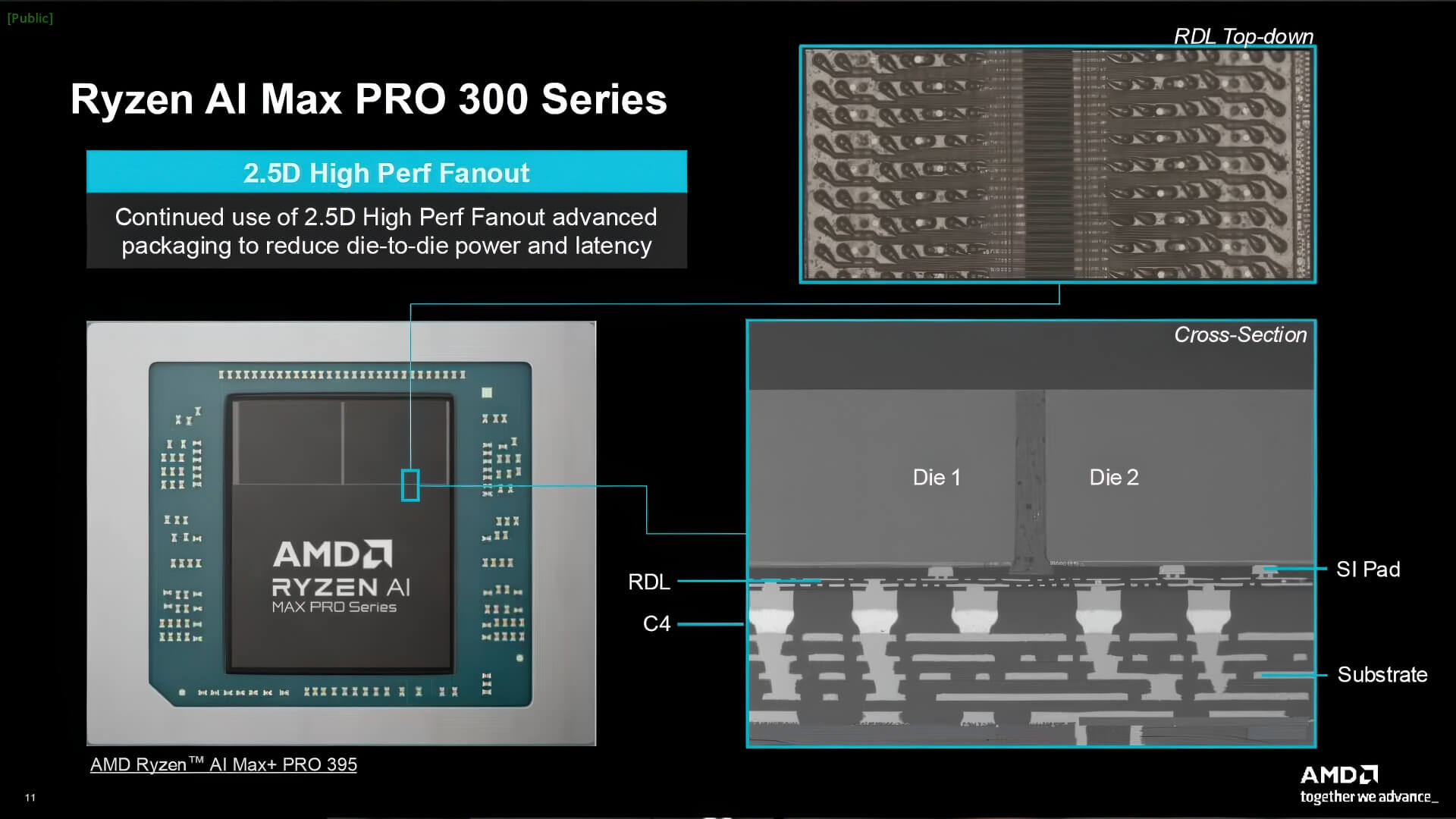

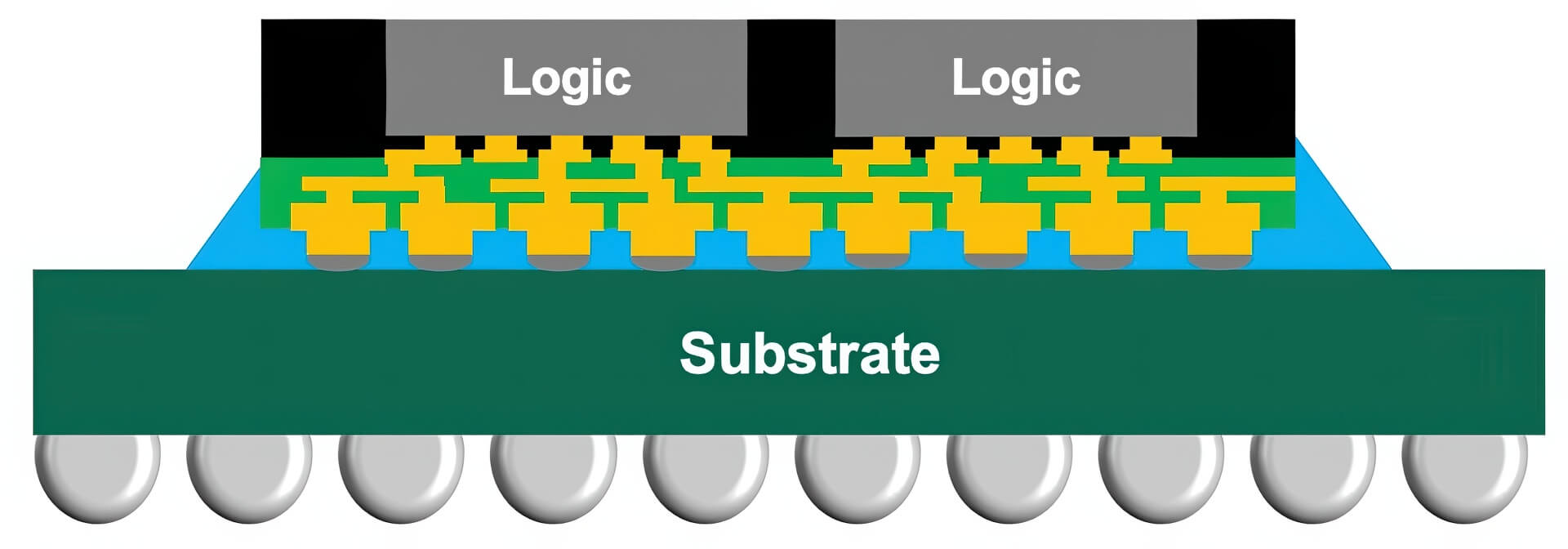

Với Strix Halo, AMD đã thử nghiệm cách tiếp cận mới thông qua công nghệ InFO-oS (Integrated Fan-Out on Substrate) kết hợp với lớp Redistribution Layer (RDL) từ TSMC. Thay vì dựa vào việc chuyển đổi dữ liệu sang dạng tuần tự, AMD sử dụng một loạt các dây dẫn song song nhỏ và ngắn để kết nối trực tiếp giữa các die.

Cách bố trí này biến lớp interposer bên dưới die thành “biển dây” – một mạng lưới kết nối rộng giúp dữ liệu di chuyển qua các cổng song song. Nhờ đó, CPU fabric có thể giao tiếp trực tiếp và hiệu quả hơn mà không cần khối SERDES cồng kềnh. Dấu hiệu rõ ràng cho thấy sự thay đổi này chính là việc các khối SERDES truyền thống biến mất, thay vào đó là một trường hình chữ nhật với nhiều pad nhỏ – đặc trưng của thiết kế fan-out.

Lợi ích và thách thức của hướng đi mới

Phương pháp Sea-of-Wires mang đến nhiều lợi ích nổi bật:

- Giảm đáng kể mức tiêu thụ năng lượng nhờ loại bỏ quá trình mã hóa/giải mã phức tạp.

- Độ trễ giảm xuống, tăng hiệu quả trong truyền tải dữ liệu.

- Băng thông dễ dàng mở rộng bằng cách bổ sung thêm cổng song song.

Tuy nhiên, kỹ thuật này cũng kéo theo những thách thức mới. Việc thiết kế và quản lý nhiều lớp RDL phức tạp hơn, đồng thời không gian dưới die trở nên hạn chế vì phải chứa thêm fan-out wiring. Điều này đòi hỏi AMD và TSMC phải có chiến lược tối ưu hóa quy trình sản xuất.

Zen 6: Bước tiến dài cho tương lai CPU AMD

Cách tiếp cận trên Strix Halo được kỳ vọng sẽ trở thành nền tảng cho toàn bộ dòng Zen 6, mang lại hiệu năng cao hơn, độ trễ thấp hơn và khả năng tiêu thụ năng lượng hiệu quả hơn. Đây là minh chứng cho thấy AMD không chỉ dựa vào tiến trình sản xuất mới mà còn đổi mới kiến trúc kết nối để nâng cao sức mạnh tổng thể.

Với bước đi này, AMD tiếp tục củng cố vị thế trong ngành bán dẫn, mở ra triển vọng cạnh tranh mạnh mẽ hơn trong kỷ nguyên mà AI và các tác vụ tính toán băng thông cao ngày càng trở nên phổ biến.