NEO Semiconductor vừa công bố 3D X-DRAM đã qua vòng proof-of-concept, nghĩa là công nghệ bộ nhớ này không còn đứng ở mức ý tưởng thuần mô phỏng. Điểm đáng chú ý của NEO 3D X-DRAM cho chip AI không phải chuyện HBM sắp bị thay thế, mà là khả năng làm DRAM dạng xếp chồng bằng hạ tầng 3D NAND sẵn có. Với bộ tăng tốc AI, đây là bài toán vì năng lực tính toán đang tăng nhanh hơn tốc độ cấp dữ liệu cho chip. Nhưng ở thời điểm này, mọi kết luận vẫn phải dừng ở mức proof-of-concept, chưa phải lời hứa thương mại.

Proof-of-concept này xác nhận điều gì về mặt kỹ thuật

Theo bài nguồn của Tom’s Hardware, test chip của NEO được chế tạo và đánh giá tại NIAR-TSRI ở Đài Loan cùng NYCU, với độ trễ đọc/ghi dưới 10 ns, giữ dữ liệu hơn 1 giây ở 85 độ C, chịu được nhiễu bit-line và word-line trên 1 giây, cùng độ bền vượt 10^14 chu kỳ.

Diễn giải ngắn gọn, NEO đang cố chứng minh hai điểm: ô nhớ của họ vẫn đủ nhanh để được xem là DRAM, và cấu trúc 3D mới chưa bộc lộ rủi ro ổn định quá lớn ở mức test chip. Mốc giữ dữ liệu hơn 1 giây trong điều kiện nhiệt cao đặc biệt đáng chú ý, vì DRAM thương mại phải refresh liên tục; nếu thời gian giữ dữ liệu tăng, áp lực điện năng và thiết kế làm tươi có thể giảm theo.

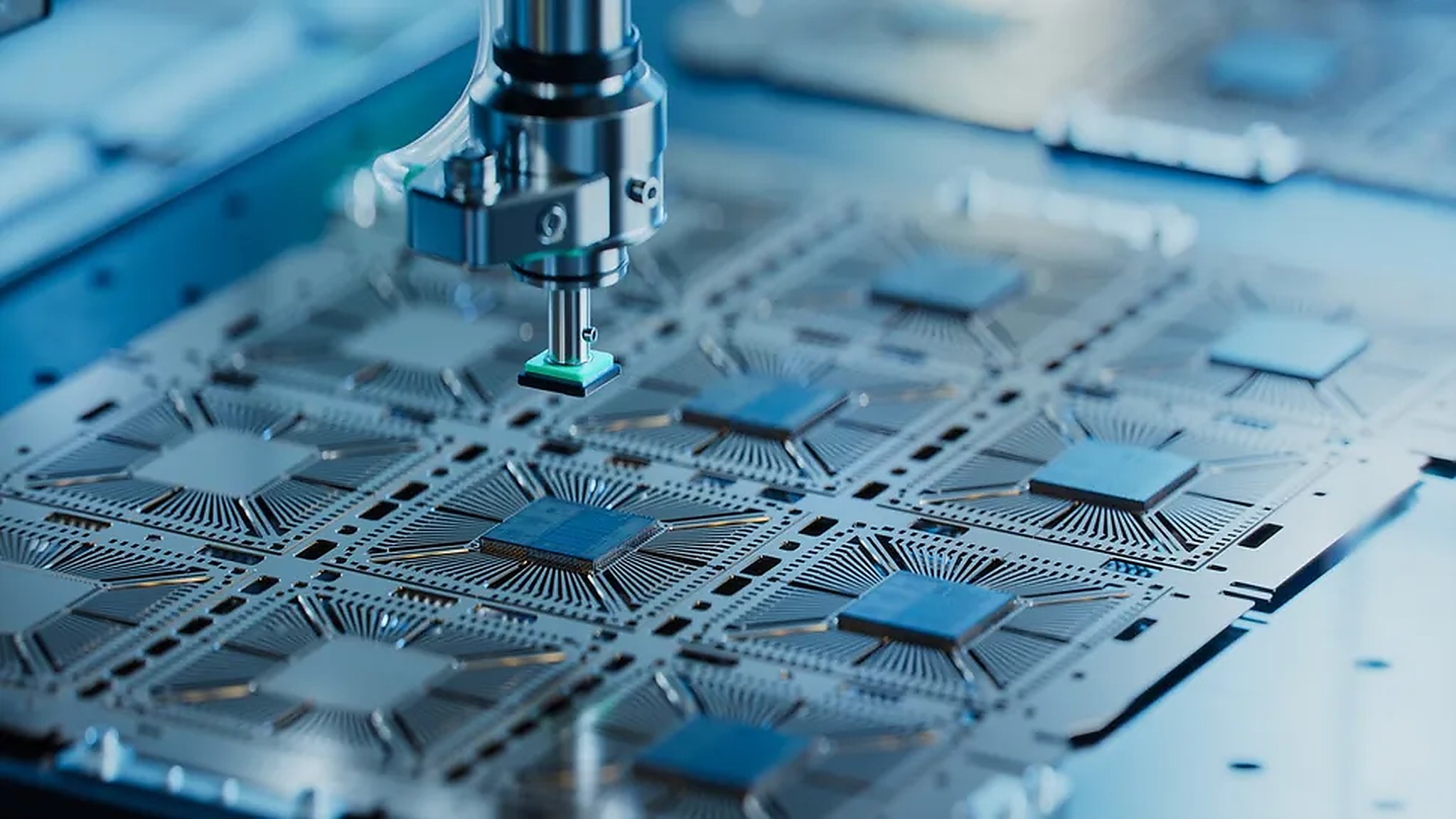

Trong thông báo của NEO Semiconductor, công ty còn nhấn mạnh test chip này dùng thiết bị, vật liệu và quy trình của 3D NAND hiện có. Đây là chi tiết đáng giá nhất, vì trở ngại lớn của công nghệ nhớ mới thường không nằm ở ý tưởng, mà ở chi phí fab và khả năng bám vào dây chuyền sản xuất có sẵn. NEO cũng nhận vốn từ Stan Shih để đi tiếp.

Điểm này cũng nối thẳng với áp lực đang thấy ở bài đơn hàng chip nhớ: khi AI kéo nhu cầu bộ nhớ tăng nhanh, một kiến trúc tận dụng hạ tầng sẵn có luôn hấp dẫn hơn phương án phải dựng hệ sinh thái fab mới.

Vì sao NEO 3D X-DRAM cho chip AI vẫn còn khá xa HBM thương mại

Dù vậy, cần tách rất rõ giữa “proof-of-concept đã qua” và “đã sẵn sàng ra thị trường”. HBM là nhiều die DRAM hoàn chỉnh được xếp chồng, nối bằng TSV và đặt sát GPU hoặc ASIC để đẩy băng thông lên rất cao; còn NEO 3D X-DRAM cho chip AI, theo mô tả hiện tại, là hướng xây mảng ô nhớ nguyên khối kiểu 3D NAND. Cùng nhắm vào nút thắt bộ nhớ cho chip AI, nhưng hai con đường này khác nhau từ cách chế tạo tới rủi ro tích hợp hệ thống.

| Điểm nhìn | Đã xác nhận | Ý nghĩa | Còn bỏ ngỏ |

| Test chip | < 10 ns, > 10^14 chu kỳ | Ý tưởng vẫn bám tiêu chí DRAM | Có giữ được khi tăng số lớp hay không |

| Sản xuất | Dựa trên quy trình 3D NAND | Giảm rủi ro đầu tư fab mới | Yield và chi phí thật ở quy mô lớn |

| Vai trò với AI | Nhắm tới mật độ cao, điện năng thấp hơn | Mở thêm lựa chọn cạnh HBM | Băng thông hệ thống chưa được chứng minh |

Chính NEO cho biết bước tiếp theo là array-level implementation, test chip nhiều lớp và tìm đối tác đồng phát triển với các hãng nhớ lớn. Nói cách khác, bài toán thương mại hóa vẫn còn nguyên: phải chứng minh yield tốt khi số lớp tăng, phải cho thấy băng thông toàn hệ thống đủ cạnh tranh, và phải thuyết phục được nhà sản xuất rằng lợi ích về chi phí hoặc điện năng đủ lớn để đáng chuyển nền tảng.

Giới hạ tầng AI vẫn phải để mắt vì nút thắt bộ nhớ ngày càng lộ rõ ở những thiết kế như TPU hai chip, nơi bài toán không còn chỉ là thêm FLOPS mà là đưa dữ liệu tới cụm tính toán rẻ hơn. Nếu NEO 3D X-DRAM cho chip AI đi được từ proof-of-concept sang sản phẩm nhiều lớp có thể sản xuất, công nghệ này mới có cơ hội trở thành mảnh ghép bổ sung cho HBM. Còn hiện tại, đây vẫn là tín hiệu kỹ thuật đáng chú ý hơn là một đối thủ HBM đã thành hình.